Nico Schottelius

# High speed NAT64 with P4

Master Thesis MA-2019-19 February 2019 to August 2019

Tutors: Alexander Dietmüller, Edgar Costa Molero, Tobias Bühler

Supervisor: Prof. Dr. Laurent Vanbever

#### **Abstract**

Due to the lack of IPv4 addresses, IPv6 deployments have recently gained in importance in the Internet. Several transition mechanisms exist that include translating IPv6 packets into IPv4 packets, thus enabling the coexistence and interoperability of both protocols.

This thesis describes an implementation of the translation mechanism NAT64, implemented in P4. Using the P4 programming language a software emulated switch was created that translates IPv4 to IPv6 and vice versa. Due to the target independence of P4 the same code can be compiled for and deployed to the FPGA hardware platform "NetFPGA".

Within the NetFPGA the NAT64 implementation achieves a stable throughput of 9.28 Gigabit/s. Our solution allows in-network translations without a router or client configurations. Due to the nature of P4, the implementation runs at line speed and thus with different hardware the same code can run potentially at much higher speeds, for instance on 100 Gbit/s switches.

# **Contents**

| 1 | Intro          | oduction                                          | 11       |

|---|----------------|---------------------------------------------------|----------|

|   | 1.1            | IPv4 Exhaustion and IPv6 Adoption                 | 11       |

|   | 1.2            | Motivation                                        | 12       |

| 2 | Bac            | kground                                           | 15       |

| _ | 2.1            | _                                                 | 15       |

|   | 2.2            | IPv6, IPv4 and Ethernet                           | 15       |

|   | 2.3            | ARP and NDP, ICMP and ICMP6                       | 16       |

|   | 2.4            | IPv6 Translation Mechanisms                       | 17       |

|   | 2.4            |                                                   | 17       |

|   |                |                                                   |          |

|   |                | 2.4.2 Stateful NAT64                              | 17       |

|   |                | 2.4.3 Higher Layer Protocol Dependent Translation | 19       |

|   |                | 2.4.4 Mapping IPv4 Addresses in IPv6              | 19       |

|   |                | 2.4.5 DNS64                                       | 20       |

|   | 2.5            | Protocol Checksums                                | 20       |

|   | 2.6            | Network Designs                                   | 22       |

|   |                | 2.6.1 IPv4 Only Network Limitations               | 22       |

|   |                | 2.6.2 Dualstack Network Maintenance               | 22       |

|   |                | 2.6.3 IPv6 Only Networks                          | 22       |

|   | 2.7            | NetFPGA                                           | 22       |

| 3 | Doo            | i mun                                             | 25       |

| 3 | <b>Des</b> 3.1 | P4/NAT64                                          | 25<br>25 |

|   | •              |                                                   | _        |

|   | 3.2            | P4/BMV2                                           | 26       |

|   | 3.3            | P4/NetFPGA                                        | 27       |

|   | 3.4            | Stateless NAT64                                   | 27       |

|   | 3.5            | Stateful NAT64                                    | 30       |

|   | 3.6            | NAT64 Verification                                | 31       |

|   | 3.7            | IPv6 and IPv4 Configuration                       | 31       |

| 4 | Res            | ults                                              | 33       |

|   | 4.1            | P4 Based Implementations                          | 33       |

|   | 4.2            | P4/BMV2                                           | 34       |

|   | 4.3            | P4/NetFPGA                                        | 34       |

|   |                | 4.3.1 Features                                    | 34       |

|   |                | 4.3.2 Stability                                   | 35       |

|   |                | 4.3.3 Usability                                   | 37       |

|   | 4.4            | Software Based NAT64                              | 38       |

|   |                | NAT64 Benchmarks                                  | 38       |

|   | 4.5            |                                                   |          |

|   |                | 4.5.1 Benchmark Design                            | 38       |

|   |                | 4.5.2 Benchmark Summary                           | 39       |

| 5 | Con            | clusion and Outlook                               | 41       |

4 CONTENTS

| Α | Resources and code repositories    | 43 |

|---|------------------------------------|----|

|   | A.1 Operating Systems              | 43 |

|   | A.2 Master Thesis                  | 43 |

|   | A.3 Xilinx Toolchain               | 43 |

|   | A.4 P4/NetFGPA Support Scripts     | 43 |

|   | A.5 P4/NetFGPA Compilation Process | 44 |

|   | A.6 P4/NetFGPA Tests               | 44 |

|   | A.6.1 Test 1: IPv4 Egress          | 44 |

|   | A.6.2 Test 2: IPv6 Egress          | 45 |

|   | A.7 P4/BMV2 Environment and Tests  | 45 |

|   | 7.7 1 4/DIVIVE ENVIRONMENTAL GOLD  | 70 |

| В | NetFPGA Logs                       | 47 |

|   | B.1 NetFPGA Flash Errors           | 47 |

|   | B.2 NetFPGA Flash Success          | 47 |

|   | B.3 NetFPGA Kernel Module          | 48 |

|   | B.4 NetFPGA Compile Logs           | 49 |

|   | 2.1 Note 1 de Compilo 2090 :       |    |

| С | Benchmark Logs                     | 57 |

|   | C.1 Enabling Hardware Offloading   | 57 |

|   | C.2 Tayga                          | 58 |

|   |                                    | 60 |

# **List of Figures**

|      | RIR IPv4 Rundown Projection [25]         |    |

|------|------------------------------------------|----|

| 1.2  | ,                                        | 12 |

| 1.3  |                                          | 12 |

| 1.4  | Separated IPv6 and IPv4 Network Segments | 13 |

| 2.1  | P4 Protocol Independence [58]            | 15 |

| 2.2  |                                          | 16 |

| 2.3  |                                          | 17 |

| 2.4  |                                          | 18 |

| 2.5  | • •                                      | 18 |

| 2.6  |                                          | 18 |

| 2.7  |                                          | 19 |

| 2.8  |                                          | 19 |

| 2.9  |                                          | 20 |

|      | IPv6 Pseudo Header                       | 21 |

| 2.11 | IPv4 Pseudo Header                       | 21 |

|      |                                          | 23 |

| 3.1  | P4 Switch Architecture                   | 25 |

| 3.2  |                                          | 26 |

| 3.3  |                                          | 26 |

| 3.4  |                                          | 27 |

| 3.5  |                                          | 28 |

| 3.6  |                                          | 29 |

| 3.7  |                                          | 30 |

| 4.1  | Hardware Test NetPFGA Card 1             | 36 |

| 4.2  |                                          | 36 |

| 4.3  |                                          | 38 |

| 4.4  |                                          | 39 |

# **List of Tables**

| 3.1 | NAT64 Match Factors               | 28 |

|-----|-----------------------------------|----|

| 3.2 | NAT64 Verification Commands       | 32 |

| 3.3 | IPv6 Address and Network Overview | 32 |

| 3.4 | IPv4 Address and Network Overview | 32 |

| 4.1 | P4/BMV2 Feature List              | 34 |

| 4.2 | P4/NetFPGA Feature List           | 35 |

| 4.3 | IPv6 to IPv4 TCP NAT64 Benchmark  | 40 |

| 4.4 | IPv4 to IPv6 TCP NAT64 Benchmark  | 40 |

| 4.5 | IPv6 to IPv4 UDP NAT64 Benchmark  | 40 |

| 4.6 | IPv4 to IPv6 UDP NAT64 Benchmark  | 40 |

# **List of Abbreviations**

ARP ..... Address Resolution Protocol

ASIC ..... Application-Specific Integrated Circuit

DAC ..... Direct Attach Cable

FGPA ..... Field-Programmable Gate Array

LPM ...... Longes Prefix Matching

MTU ..... Maximum Transfer Unit

NAT ..... Network Address Translation

NAT64 ...... Network Address Translation from / to IPv6 to / from IPv4

NDP ....... Neighbor Discovery Protocol RIR ...... Regional Internet Registry

RTT ..... Round Trip Time

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

## Declaration of originality

The signed declaration of originality is a component of every semester paper, Bachelor's thesis, Master's thesis and any other degree paper undertaken during the course of studies, including the respective electronic versions.

Lecturers may also require a declaration of originality for other written papers compiled for their courses.

I hereby confirm that I am the sole author of the written work here enclosed and that I have compiled it in my own words. Parts excepted are corrections of form and content by the supervisor.

Title of work (in block letters):

HIGH SPEED NATEY WITH 84

| <b>Authored by</b> (in block letters): For papers written by groups the names of all auth                                                                                                       | nors are required.                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Name(s):                                                                                                                                                                                        | First name(s):                                                            |

| SCHOTTELIUS                                                                                                                                                                                     | NICO                                                                      |

|                                                                                                                                                                                                 |                                                                           |

|                                                                                                                                                                                                 |                                                                           |

|                                                                                                                                                                                                 |                                                                           |

|                                                                                                                                                                                                 |                                                                           |

| \\/\!\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                                                                                                                                          |                                                                           |

| <ul> <li>I have committed none of the forms sheet.</li> <li>I have documented all methods, dat</li> <li>I have not manipulated any data.</li> <li>I have mentioned all persons who w</li> </ul> | rere significant facilitators of the work.                                |

| <ul><li>I have documented all methods, dat</li><li>I have not manipulated any data.</li></ul>                                                                                                   | ra and processes truthfully.  There significant facilitators of the work. |

For papers written by groups the names of all authors are required. Their signatures collectively guarantee the entire content of the written paper.

# **Chapter 1**

# Introduction

In this chapter we give an introduction about the topic of the master thesis, the motivation, and problems that we address. We explain the current state of IPv4 exhaustion and IPv6 adoption and describe how it motivates our work to support to ease transition to IPv6 networks.

# 1.1 IPv4 Exhaustion and IPv6 Adoption

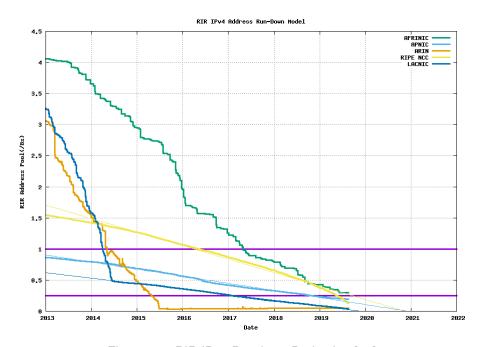

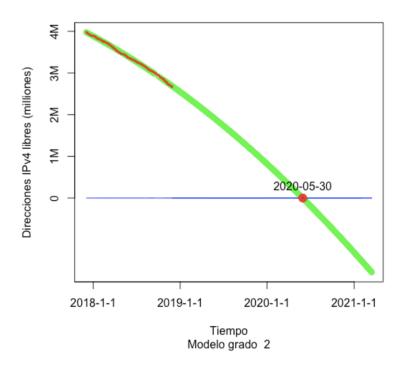

The Internet has almost completely run out of public IPv4 space. The 5 Regional Internet Registries (RIRs) report IPv4 exhaustion worldwide [48], [4], [27], [1], [5]. Figure 1.1 contains summarised data from all RIRs and projects complete IPv4 addresses depletion by 2021. The LACNIC project even predicts complete exhaustion for 2020 as shown in figure 1.2.

Figure 1.1: RIR IPv4 Rundown Projection [25]

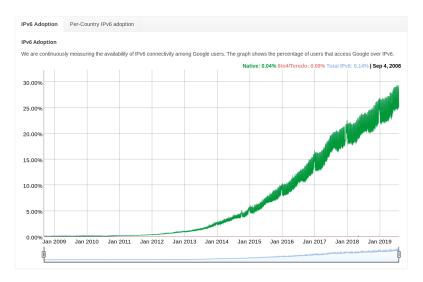

On the other hand, IPv6 adoption grows significantly, with at least three countries (India, US, Belgium) surpassing 50% adoption [2], [60], [13]. Traffic from Google users reaches almost 30% as of 2019-08-08 [21], see figure 1.3.

We conclude that IPv6 is a technology strongly gaining importance. IPv4 depletion is estimated to be happening worldwide in the next years. Thus more devices will be using IPv6, while communication with legacy IPv4 devices still needs to be provided.

Figure 1.2: LACNIC Exhaustion Projection [27]

## 1.2 Motivation

Figure 1.3: Google IPv6 Statistics [21]

IPv6 hosts and IPv4 hosts cannot directly connect to each other, because the protocols are incompatible to each other. To allow communication between different protocol hosts, several transition mechanisms have been proposed [62], [39]. However installation and configuration of the transition mechanism usually require in-depth knowledge about both protocols and require additional hardware to be added in the network. In this thesis we show an in-network transition method based on NAT64 [6]. Compared to traditional NAT64 methods which require hosts to explicitly use an extra device in the network, our proposed method is transparent to the hosts. This way the routing and network configuration does not need to be changed to support NAT64 within a network. Currently network operators have to focus on two network stacks when designing networks: IPv6 and IPv4. While in a small scale setup this might not introduce significant

<sup>&</sup>lt;sup>1</sup>Usually the default router will take this role.

1.2 Motivation 13

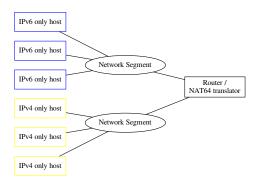

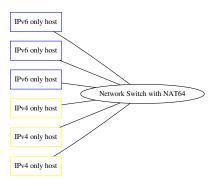

Figure 1.4: Separated IPv6 and IPv4 Network Segments

complexity, figure 1.4 shows how the complexity quickly grows even with a small number of hosts. The proposed in-network solution does not only ease the installation and deployment of IPv6, but it also allows line speed translation, because it is compiled into target dependent low level code that can run in ASICs [37], FPGAs [34] or even in software [10]. Figure 3.3 shows how the design differs for an in-network solution. Even on fast CPUs, software solutions like Tayga [29] can be CPU bound (see section 4.4) and are incapable of translating protocols at line speed.

# **Chapter 2**

# **Background**

In this chapter we describe the key technologies involved and their relation to our work.

#### 2.1 P4

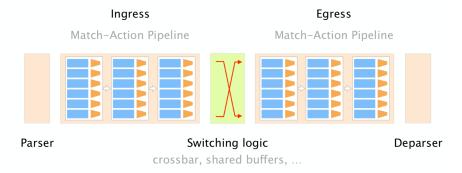

P4 is a programming language designed to program inside network equipment. Its main features are protocol and target independence. The *protocol independence* refers to the separation of concerns in terms of language and protocols: P4, generally speaking, operates on bits that are parsed and then accessible in the self defined structures called headers. The general flow can be seen in figure 2.1: a parser parses the incoming packet and prepares it for processing in the switching logic. Afterwards the packets are output and deparsing of the parsed data might follow. In the context of NAT64 this is a very important feature: while the parser will read and parse in the ingress pipeline one protocol (f.i. IPv6), the deparser will output a different protocol (f.i. IPv4). The *target independence* is the second major feature of P4: it allows code

Figure 2.1: P4 Protocol Independence [58]

to be compiled to different targets. While in theory the P4 code should be completely target independent, in reality, there are some modifications needed on a per-target basis and each target faces different restrictions. The challenges arising from this are discussed in section 4.1. As opposed to general purpose programming languages, P4 lacks some features. Most notably loops, floating point operations and modulo operations. However, within its constraints, P4 can guarantee operation at line speed, which general purpose programming languages cannot quarantee and also fail to achieve in reality (see section 4.4 for details).

# 2.2 IPv6, IPv4 and Ethernet

The first IPv6 RFC was published in 1998 [17]. Both IPv6 and IPv4 operate on layer 3 of the OSI model. In this thesis we only consider transmission via Ethernet, which operates at layer 2. Inside the Ethernet frame a field named "type" specifies the higher level protocol identifier. This

<sup>&</sup>lt;sup>1</sup>0x0800 for IPv4 [24] and 0x86DD for IPv6 [15].

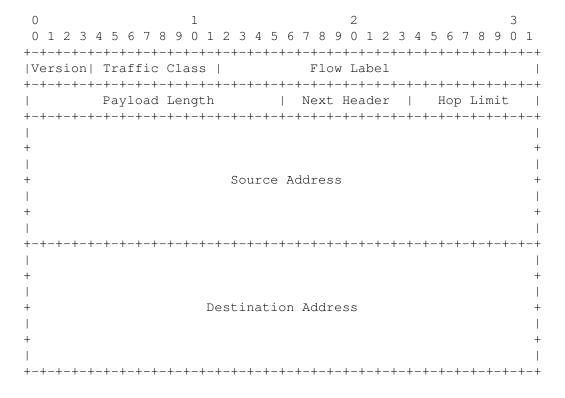

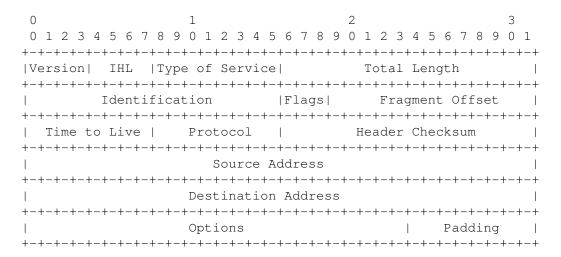

is important because Ethernet can only reference one protocol, which makes IPv4 and IPv6 mutually exclusive. In the figures 2.5 and 2.4 we show the packet headers of IPv4 and IPv6 for showing the in-protocol differences. The most notable differences between the two protocols for this thesis are:

Different address lengths

IPv4: 32 bitIPv6: 128 bit

- Lack of a checksum in IPv6

- Format of Pseudo headers (see section 2.5)

# 2.3 ARP and NDP, ICMP and ICMP6

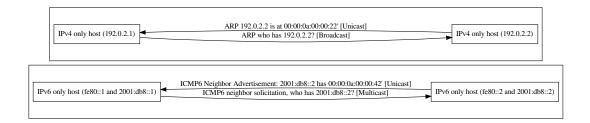

While IPv6 and IPv4 are primarily used as a "shell" to support addressing for protocols that have no or limited addressing support (like TCP or UDP), protocols like ARP [40] and NDP [33] provide support for resolving IPv6 and IPv4 addresses to hardware (MAC) addresses. While both ARP and NDP are only used prior to establishing a connection and their results are cached, their availability is crucial for operating a switch, because without ARP or NDP no connection will every be established. Figure 2.2 illustrates a typical address resolution process. The major

Figure 2.2: ARP and NDP

differences between ARP and NDP in relation to P4 are

- ARP is a separate protocol on the same layer as IPv6 and IPv4,

- NDP operates below ICMP6 which operates below IPv6,

- NDP contains checksums over payload,

- and NDP in ICMP6 contains optional, non-referenced option fields (specifically: ICMP6 link layer address option).

ARP is required to be a separate protocol, because IPv4 hosts don't know how to communicate with each other yet, as they don't have a way to communicate to the target IPv4 address ("The chicken and the egg problem"). NDP on the other hand already works within IPv6, as every IPv6 host is required to have a self-assigned link local IPv6 address from the IPv6 network fe80::/10 (compare RFC4291 [23]). While ARP uses broadcasting for address resolution, NDP uses multicasting. IPv6 hosts automatically join multicast groups that embed parts of their IPv6 addresses [16], [64]. This way the collision domain is significantly reduced in IPv6, compared to IPv4.

As seen later in this document (compare section 4.3.1), the requirement to generate checksums over payload poses difficult problems for some hardware targets. Even more difficult is the use of options within ICMP6. The problem arises from the layout of the options, as seen in figure 2.3 and the following quote:

Figure 2.3: ICMP6 Option Fields

"Neighbor Discovery messages include zero or more options, some of which may appear multiple times in the same message. Options should be padded when necessary to ensure that they end on their natural 64-bit boundaries".<sup>2</sup>

ICMP6 and ICMP are primarily used to signal errors in communication. Specifically, signalling that a packet is too big to pass a certain link and needs fragmentation is a common functionality of both protocols. For a host (or a switch) to be able to emit ICMP6 and ICMP messages, the host requires a valid IPv6 / IPv4 address. Without ICMP6 / ICMP support path MTU discovery [32], [30] does not work and the sender needs to determine different ways of finding out the maximum MTU on the path.

### 2.4 IPv6 Translation Mechanisms

While in this thesis we focus on NAT64 as a translation mechanism, there are a variety of different approaches, some of which we would like to portray here.

#### 2.4.1 Stateless NAT64

Stateless NAT64 describes static mappings between IPv6 and IPv4 addresses. This can be based on longest prefix matching (LPM), ranges, bitmasks or individual entries. NAT64 translations as described in this thesis modify multiple layers in the translation process:

- Ethernet (changing the type field)

- IPv4 / IPv6 (changing the protocol, changing the fields)

- TCP/UDP/ICMP/ICMP6 checksums

Figures 2.4 and 2.5 show the headers of IPv4 and IPv6. As can be seen in the diagrams not only are the addresses of different size, but fields have also been changed or removed when the version changed. Depending on the NAT64 translation direction, a translator will need to re-arrange fields to a different position, remove fields and add fields. This in turn causes the packet size for standard headers to differ by 160 Bit.<sup>3</sup>

#### 2.4.2 Stateful NAT64

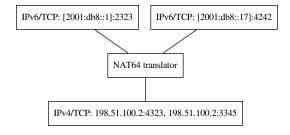

Stateful NAT64 as defined in RFC6146 [6] defines how to create 1:n mappings between IPv6 and IPv4 hosts. The motivation for stateful NAT64 is similar to stateful NAT44 [54]: while NAT44 allows translating many (private) IPv4 addresses to one (public) IPv4 address, NAT64 allows translating many IPv6 addresses to one IPv4 address. While the opposite stateful translation, mapping many IPv4 addresses to one IPv6 address, is also technically possible, the differences in address space size don't justify its use in general.

Stateful NAT64 in particular uses information in higher level protocols to multiplex connections: Given one IPv4 address and the TCP protocol, outgoing connections from IPv6 hosts can dynamically mapped to the range of possible TCP ports. After a session is closed, the port can be reused again. The selection of mapped ports is usually based on the availability of the IPv4 side and not related to the original port. To support stateful NAT64, the translator needs to store the mapping in a table and purge entries regularly.

Stateful NAT64 usually uses information found in protocols at layer 4 like TCP [44] or UDP [41]. However, it can also support ICMP [42] and ICMP6 [14].

<sup>&</sup>lt;sup>2</sup>Quote from [33].

<sup>&</sup>lt;sup>3</sup>IPv6: 320 Bit, IPv4 160 Bit

Figure 2.4: IPv6 Header [17]

Figure 2.5: IPv4 Header [43]

Figure 2.6: Stateful NAT64

### 2.4.3 Higher Layer Protocol Dependent Translation

Further translation can be achieved by using information in higher level protocols like HTTP [19] or TLS [9]. Application proxies like nginx [38] use layer 7 protocol information, like the requested hostname, to proxy towards backends.

Within this proxying method, the underlying IP protocol can be changed from IPv6 to IPv4 and vice versa. However, if using HTTPS with TLS 1.3 [46], the requested hostname that is usually used for selecting the backend can be encrypted, which poses a challenge for implementations. While protocol dependent translation has the highest amount of information to choose from for translation, complex parsers or even cryptographic methods are required for it. That reduces the opportunities for) protocol dependent translations to run on devices with less sophisticated devices.

## 2.4.4 Mapping IPv4 Addresses in IPv6

As described in section 2.2, one of the major differences between IPv6 and IPv4 is the address length. As the whole IPv4 Internet can be represented in only 32 bits, it is a common practice to assign an IPv6 prefix for IPv6 hosts that represents a mapping to the whole IPv4 Internet. In RFC6052 [8] the well known prefix 64:ff9b::/96 is defined that can be used for this purpose. One possibility to map an IPv4 address into the prefix is by adding its integer value to the prefix, treating it as an offset. In figure 2.7 we show example python code of how this can be done. Network administrators can choose to use either the well known prefix or to use a

```

>>> import ipaddress

>>> prefix=ipaddress.IPv6Network("64:ff9b::/96")

>>> ipv4address=ipaddress.IPv4Address("192.0.2.0")

>>> int(ipv4address)

3221225984

>>> hex(3221225984)

'0xc0000200'

>>> prefix[int(ipv4address)]

IPv6Address('64:ff9b::c000:200')

```

Figure 2.7: Representing an IPv4 address in an IPv6 Prefix

network block of their own to map the Internet.<sup>4</sup> While a /96 prefix seems a natural selection (it provides exactly 32 bit), other prefix lengths are defined in RFC6052 (see figure 2.8) that allow flexible embedding of the IPv4 address. RFC6146, which describes stateful NAT64, states

| PL  0- |        | +++                 | -56  | 64  |         | 8896- |        |  |

|--------|--------|---------------------|------|-----|---------|-------|--------|--|

| 32     | 1      | ++<br> v4(32)<br>++ |      | l u | suffix  |       |        |  |

| 40     |        | v4 (24)             |      | l u | (8)  su | ffix  |        |  |

| 48     | prefix | v4<br>  v4          | (16) | l u | (16)    | suffi |        |  |

| 56     | prefix | ++                  | (8)  | l u | v4 (24  | )   s | uffix  |  |

| 64     |        | ++                  |      | l u | v4 (3   | 2)    | suffix |  |

| 1961   | prefix | ++                  |      |     |         |       | v4(32) |  |

Figure 2.8: IPv4 Embedding Depending on the Prefix Length

<sup>&</sup>lt;sup>4</sup>For instance 2a0a:e5c0:0:1::/96 [57].

that "IPv4 addresses of IPv4 hosts are algorithmically translated to and from IPv6 addresses by using the algorithm defined in [RFC6052]" [6] While this sentence does not use the typical RFC keywords like SHALL, REQUIRED, etc. [12], we interpret this sentence in the meaning of "a stateful NAT64 translator SHALL implement IPv4 address embedding as described in the algorithm of RFC6052".

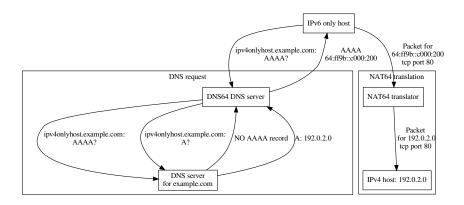

#### 2.4.5 DNS64

Tightly related to NAT64 is a technology known as DNS64 [7]. DNS64 tries to solve the problem of addressing IPv4 only hosts from IPv6 only hosts by adding a "fake" IPv6 (AAAA) DNS resource record, as shown in figure 2.9. The DNS64 DNS server will query the authorita-

Figure 2.9: Illustration of DNS64

tive DNS server for an AAAA record. However as the host *ipv4onlyhost.example.com* is only reachable by IPv4, it also only has an A entry. After receiving the answer that there is no AAAA record, the DNS64 server will ask for an A record and will get an answer that the name *ipv4onlyhost.example.com* resolves to the IPv4 address *192.0.2.0*. The DNS64 server then embeds the IPv4 address in the configured IPv6 prefix (*64:ff9b::/96* in this case) and returns a fake AAAA record to the IPv6 only host (pointing to *64:ff9b::c000:200* in this case). The IPv6 only host then will use the address to connect to. The NAT64 translator recognises either that the address is part of a configured prefix or that it has a dedicated table entry for mapping this IPv6 address to an IPv4 address and translates it accordingly.

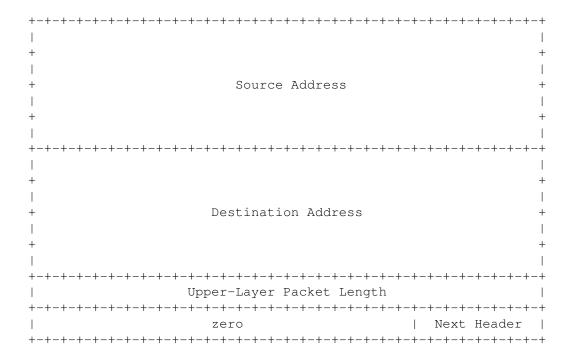

#### 2.5 Protocol Checksums

One challenge for translating IPv6 to IPv4 are checksums of higher level protocols like TCP and UDP that incorporate information from the lower level protocols. The pseudo header for upper layer protocols for IPv6 is defined in RFC2460 [17] and shown in figure 2.10, the IPv4 pseudo header for TCP and UDP are defined in RFC768 and RFC793 and are shown in 2.11. When translating, the checksum fields in the higher protocols need to be adjusted. The checksums for TCP and UDP are calculated not only over the pseudo headers, but also contain the payload of the packet. This is important because some targets (like the NetFPGA) do not allow accessing the payload (see section 3.3). The checksums for IPv4, TCP, UDP and ICMP6 are all based on the "Internet Checksum" [43], [11]. Its calculation can be summarised as follows:

The checksum field is the 16-bit one's complement of the one's complement sum of all 16-bit words in the header. For purposes of computing the checksum, the value of the checksum field is zero.<sup>5</sup>.

<sup>&</sup>lt;sup>5</sup>Quote from Wikipedia [61].

Figure 2.10: IPv6 Pseudo Header

| 0  |      | 7 8     | 15 1   | 6 23    | 3 24   | 31 |

|----|------|---------|--------|---------|--------|----|

| +- |      | -+      | +      |         |        | +  |

|    |      | sourc   | e add: | ress    |        |    |

| +- |      | -+      | +      |         |        | +  |

|    |      | destina | tion a | address | 5      |    |

| +- |      | -+      | +      |         |        | +  |

|    | zero | protoc  | ol  To | CP/UDP  | length |    |

| +- |      | _+      | +      |         |        | +  |

Figure 2.11: IPv4 Pseudo Header

# 2.6 Network Designs

In relation to IPv6 and IPv4, there are in general three different network designs possible: The oldest form are IPv4 only networks. These networks consist of hosts that are either not configured for IPv6 or are even technically incapable of enabling the IPv6 protocol. These nodes are connected to an IPv4 router that is connected to the Internet. That router might be capable of translating IPv4 to IPv6 and vice versa.

With the introduction of IPv6, hosts can have a separate IP stack active and in that configuration hosts are called "dualstack hosts". Dualstack hosts are capable of reaching both IPv6 and IPv4 hosts directly without the need of any translation mechanism.

The last possible network design is based on IPv6 only hosts. While it is technically easy to disable IPv4, completely removing the IPv4 stack in current operating systems is not an easy task [56]. While the three network designs look similar, there are significant differences in operating them and limitations that are not easy to circumvent. In the following sections, we describe the limitations and explain how a translation mechanism like our NAT64 implementation should be deployed.

### 2.6.1 IPv4 Only Network Limitations

As shown in figures 2.5 and 2.4 the IPv4 address size is 32 bit, while the IPv6 address size is 128 bit. Without an extension to the address space, there is no protocol independent mapping of IPv4 address to IPv6<sup>6</sup> that can cover the whole IPv6 address space. Thus IPv4 only hosts can never address every host in the IPv6 Internet. While protocol dependent translations can try to minimise the impact, accessing all IPv6 addresses independent of the protocol is not possible.

#### 2.6.2 Dualstack Network Maintenance

While dualstack hosts can address any host in either IPv6 or IPv4 networks, the deployment of dualstack hosts comes with a major disadvantage: all network configurations double. The required routing tables double, the firewall rules roughly double<sup>7</sup> and the number of network supporting systems, (like DHCPv4, DHCPv6, router advertisement daemons, etc.) also roughly double. Additionally, services that run on either IPv6 or IPv4 might need to be configured to run in dualstack mode as well and not every software might be capable of that. So while there is the instant benefit of not requiring any transition mechanism or translation method, we argue that the added complexity (and thus operational cost) of running dual stack networks can be significant.

### 2.6.3 IPv6 Only Networks

IPv6 only networks are in our opinion the best choice for long term deployments. Our reasons for this are the following: First of all hosts eventually will need to support IPv6 and secondly IPv6 hosts can address the whole 32 bit IPv4 Internet mapped in a single /96 IPv6 network. IPv6 only networks also allow the operators to focus on one IP stack.

### 2.7 NetFPGA

The NetFPGA [65] is an FPGA card featuring four 10 Gbit/s SFP+ ports. It includes the Xilinx Virtex-7 690T FPGA on board, 27 MB of storage, to save table data, and 8 GB of DDR3 RAM. The NetFPGA can be run inside a host (connected by PCI-E, gen 3) or as a standalone card. It can be used as a "traditional" FPGA, with the focus on designing the logic. However, the NetFPGA also supports the P4 programming language [34] and thus abstracts away the low level logic by providing a higher level interface. For the purpose of this thesis we treat the NetFPGA as a standard P4 target, similar to other available P4 targets [37], [36], [35]. In particular, we

<sup>&</sup>lt;sup>6</sup>See section 2.2.

<sup>&</sup>lt;sup>7</sup>The rule sets even for identical policies in IPv6 and IPv4 networks are not identical, but similar. For this reason we state that roughly double the amount of firewall rules are required for the same policy to be applied.

2.7 NetFPGA 23

Figure 2.12: NetFPGA Board [65]

treat the NetFPGA as a P4 capable, four port 10 Gbit/s network switch that allows us to process packets at line speed.

# **Chapter 3**

# Design

In this chapter we describe the architecture of our solution and our design choices. We first introduce the general design of NAT64 in the P4 architecture. Afterwards we describe the design differences of the BMV2 and NetFPGA P4 architectures. Afterwards we discuss the design of stateless and stateful NAT64 in relation to P4 as well as two existing software NAT64 solutions. Lastly we discuss how we verify NAT64 functionality and present the network configurations that we use.

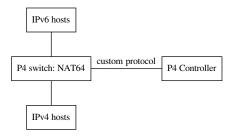

### 3.1 P4/NAT64

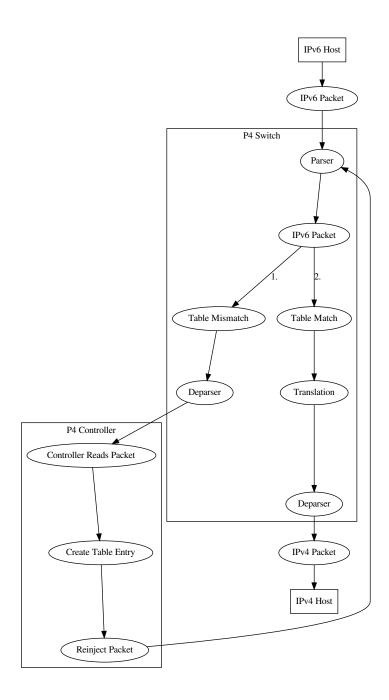

Figure 3.1: P4 Switch Architecture

In section 2.4 we discussed different translation mechanisms for IPv6 and IPv4. In this thesis we focus on the translation mechanisms "stateless" and "stateful" NAT64. While higher layer protocol dependent translations are more flexible, this topic has already been addressed in [53] and the focus in this thesis is on the practicability of high speed NAT64 with P4. The high level design can be seen in figure 3.1: a P4 capable switch is running our code to provide NAT64 functionality. A P4 switch cannot manage its tables on its own and needs support for this from a controller. The controller also has the role to handle unknown packets and can modify the runtime configuration of the switch. This is especially useful in the case of stateful NAT64. If only static table entries are required, they can usually be added at the start of a P4 switch and the controller can also be omitted. However, stateful NAT64 requires the use of a controller to create session entries in the switch tables. The P4 switch can use any protocol to communicate with the controller, as the connection to the controller is implemented as a separate Ethernet port

Software NAT64 solutions typically require routing to be applied to transport the packet to the NAT64 translator as shown in figure 3.2.

Our design differs here: while routing could be used like described above, NAT64 with P4 does not require any routing to be setup. Figure 3.3 shows the network design that we realise using P4. This design has multiple advantages: first it reduces the number of devices to pass and thus directly reduces the RTT, secondly it allows translation of IP addresses within the same

26 CHAPTER 3. DESIGN

Figure 3.2: Standard NAT64 Translation

logic network segment. P4 switches in general look very similar to regular switches, however

Figure 3.3: In-network NAT64 Translation

support executing logic while the packet passes through the switch. Figure 3.4 illustrates how our solution is implemented and translates packets.

#### 3.2 P4/BMV2

The software emulated switch that is implemented using Open vSwitch [20] and the behavioral model [10] offers the fastest and easiest way of P4 development. All NAT64 features are tested first on P4/BMV2 and in a second step ported to P4/NetFPGA and modified, where necessary. The development follows closely the general design shown in section 3.1. As outlined in section 2.5, checksums inside higher level protocols need to be adjusted after translation. Within the software emulation checksums can be computed with two different methods:

- Recalculating the checksum by inspecting headers and payload

- Calculating the difference between the translated headers

The BMV2 model is sophisticated and provides direct support for calculating the checksum over the payload. This allows the BMV2 model to operate as a full featured host, including advanced features like responding to ICMP6 Neighbor discovery requests [33] that include payload checksums. Sample code that calculates the required checksum for answering NDP queries is shown in figure 3.5. The code shows how the field hdr.icmp6.checksum is updated with the csum16 method depending on the IPv6 and ICMP6 headers as well as the payload. The second option of using the differences is described in section 3.3.

3.3 P4/NetFPGA 27

Figure 3.4: Our P4 Switch Architecture

## 3.3 P4/NetFPGA

While the P4-NetFPGA project [34] allows compiling P4 to the NetFPGA, the design slightly varies due to limitations in the available toolchain. In particular, the NetFPGA P4 compiler does not support reading the payload. For this reason it also does not support creating the checksum based on the payload. To support checksum modifications in NAT64 on the NetFPGA, the checksum is calculated using differences between the IPv6 and IPv4 headers.

As the checksum calculation only depends on the 1-complement sums of headers and the payload (compare section 2.5) and only headers are modified during NAT64 translations, the higher level protocol checksums can be corrected based on the sum of differences of both headers. Thus our P4/NetFPGA implementation first calculates the sum of the relevant IPv4 headers (v4sum()), the sum of the relevant IPv6 headers (v6sum()) and then calculates the difference including a possible carry bit and adjusts the higher level protocol by this difference ( $delta_tcp_from_v6_to_v4()$ ). Figure 3.6 shows an excerpt of the code used for adjusting the checksum when translating TCP from IPv6 to IPv4. It is notable that not the full headers are used, but only a "pseudo header" is (compare figures 2.10 and 2.11).

#### 3.4 Stateless NAT64

As seen in section 2.4.1, stateless NAT64 can be implemented using various factors. Our design for the stateless depends on the capabilities of the environment and is summarised in table 3.1. When using LPM for translating from IPv6 to IPv4, a /96 IPv6 network is configured for covering the whole IPv4 Internet and the individual IPv4 address is appended to the prefix (compare section 3.7). We also use LPM to match on an IPv4 sub network that translates to an IPv6 sub network. Individual entries are configured differently depending on the implementation: Limitations in the P4/NetFPGA environment require to use table entries. Jool supports individual entries as a special case of LPM, with a network mask matching only one IP address. Tayga supports LPM to translate from IPv6 to IPv4, but requires individual entries for translating from IPv4 to IPv6. Our P4/BMV2 offers the highest degree of flexibility, as it provides support for

<sup>&</sup>lt;sup>1</sup>This feature could be implemented in theory, but isn't available at the moment, see [51].

28 CHAPTER 3. DESIGN

```

/* checksumming for icmp6_na_ns_option */

update_checksum_with_payload(meta.chk_icmp6_na_ns == 1,

/* 128 */

hdr.ipv6.src_addr,

/* 128 */

hdr.ipv6.dst_addr,

/* 32 */

meta.cast_length,

24w0,

/* 24 0's */

PROTO_ICMP6,

/* 8 */

hdr.icmp6.type,

/* 8 */

hdr.icmp6.code,

/* 8 */

hdr.icmp6_na_ns.router,

hdr.icmp6_na_ns.solicitated,

hdr.icmp6_na_ns.override,

hdr.icmp6_na_ns.reserved,

hdr.icmp6_na_ns.target_addr,

hdr.icmp6_option_link_layer_addr.type,

hdr.icmp6_option_link_layer_addr.ll_length,

hdr.icmp6_option_link_layer_addr.mac_addr

},

hdr.icmp6.checksum,

HashAlgorithm.csum16

);

```

Figure 3.5: P4/BMV2 Checksumming

| Implementation | NAT64 match                                              |

|----------------|----------------------------------------------------------|

| P4/BMV2        | LPM (both directions)                                    |

|                | and individual entries (both directions)                 |

| P4/NetPFGA     | Individual entries                                       |

| Tayga          | LPM (IPv6 to IPv4) and individual entries (IPv4 to IPv6) |

| Jool           | LPM (both directions)                                    |

Table 3.1: NAT64 Match Factors

3.4 Stateless NAT64 29

```

action v4sum() {

bit<16> tmp = 0;

tmp = tmp + (bit<16>) hdr.ipv4.src_addr[15:0];

// 16 bit

tmp = tmp + (bit<16>) hdr.ipv4.src_addr[31:16];

// 16 bit

tmp = tmp + (bit<16>) hdr.ipv4.dst_addr[15:0];

// 16 bit

tmp = tmp + (bit<16>) hdr.ipv4.dst_addr[31:16];

// 16 bit

// 16 bit

tmp = tmp + (bit<16>) hdr.ipv4.totalLen -20;

tmp = tmp + (bit<16>) hdr.ipv4.protocol;

// 8 bit

meta.v4sum = ~tmp;

}

/* analogue code for v6sum skipped */

action delta_tcp_from_v6_to_v4()

v6sum();

v4sum();

bit<17> tmp = (bit<17>) hdr.tcp.checksum + (bit<17>) meta.v4sum;

if (tmp[16:16] == 1) {

tmp = tmp + 1;

tmp[16:16] = 0;

tmp = tmp + (bit<17>) (0xffff - meta.v6sum);

if (tmp[16:16] == 1) {

tmp = tmp + 1;

tmp[16:16] = 0;

hdr.tcp.checksum = (bit<16>) tmp;

}

```

Figure 3.6: Calculating Checksum based on Header Differences

30 CHAPTER 3. DESIGN

individual entries based on table entries and LPM table entries.

## 3.5 Stateful NAT64

Figure 3.7: Stateful NAT64 with P4

Similar to stateless NAT64, the design of stateful NAT64 depends on the features of the individual implementation. As pointed out in section 2.4.2, stateful NAT64 is very similar to stateless NAT64, with the main difference being an additional stateful table that helps to create 1:n mappings. We use different approaches within the implementations to solve this problem:

• For P4/BMV2 and P4/NetPFGA a python controller handles packets that don't have a table entry, sets the table entry in the P4 switch and inserts the original packet afterwards back

3.6 NAT64 Verification 31

into the switch.

With Tayga we rely on the Linux kernel NAT44 capabilities

Jool implements its own stateful mechanism based on port ranges

All methods though operate in a very similar fashion: A "controller" inspects the IPv6 packet and depending on the source address, destination address, protocol (TCP, UDP, ICMP, ICMP6, etc.) and the protocol ID (source / destination TCP/UDP port, ICMP identifier) it selects an outgoing IPv4 address, and source port or ICMP identifier. In case of Jool and Tayga this decision is based on a session table inside the Linux kernel, in case of P4 this decision is based on a session table inside the python controller. While the Jool and Tayga both support cleaning up old session entries, our P4 based solution does not support this feature at the moment.

In figure 3.7 we show the flow of a packet for stateful translation in a P4 switch in detail. An IPv6 only host emits a packet that should be translated to IPv4. On a new connection there will be no table entry in the P4 switch to match. Thus the table mismatch causes the P4 switch to forward the packet to the controller. The controller then inspects the packet, creates a table entry for the session and reinjects the packet into the P4 switch. The P4 switch then processes the packet again, however this time it finds a matching table entry. This entry causes translation to happen to a specific IPv4 address, including higher level protocol changes. After processing the IPv6 packet it is output as a translated IPv4 packet. A second packet of the same session will directly take the second path via table match, as the session ID will stay the same.<sup>2</sup> This is an important feature, because if the controller was involved into processing every packet, the P4 controller would become the bottleneck.

### 3.6 NAT64 Verification

We use socat [47] to verify basic operation of the NAT64 gateway and iperf [18] to test stability of the implementation and measure bandwidth. In particular we use the commands listed in table 3.2. The socat commands allow interactive testing on TCP and UDP connections, while the iperf commands fully utilise the available bandwidth with test data. The socat and iperf commands are used to verify all three NAT64 implementations (P4, Tayga, Jool).

# 3.7 IPv6 and IPv4 Configuration

The following sections refer to host and network configurations. In this section we describe the IPv6 and IPv4 configurations as a basis for the discussion.

All IPv6 addresses are from the documentation block 2001:DB8::/32 [26]. In particular we use the sub networks and IPv6 addresses shown in table 3.3.

We use private IPv4 addresses as specified by RFC1918 [45] from the 10.0.0.0/8 range as shown in table 3.4.

<sup>&</sup>lt;sup>2</sup>We use the quintuple (source address, destination address, source port, destination port, protocol) to generate a unique ID.

| Command                  | Example                                 | Description             |

|--------------------------|-----------------------------------------|-------------------------|

| socat - TCP6:HOST:PORT   | socat - TCP6:[2001:db8:42::a00:2a]:2345 | Connect via IPv6/TCP    |

|                          |                                         | to IPv4 host            |

| socat - UDP6:HOST:PORT   | socat - UDP6:[2001:db8:42::a00:2a]:2345 | Connect via IPv6/UDP    |

|                          |                                         | to IPv4 host            |

| socat - TCP:HOST:PORT    | socat - TCP:10.0.1.42:2345              | Connect via IPv4/TCP    |

|                          |                                         | to IPv6 host            |

| socat - UDP:HOST:PORT    | socat - UDP:10.0.1.42:2345              | Connect via IPv4/UDP    |

|                          |                                         | to IPv6 host            |

| socat - UDP6-LISTEN:PORT | socat - UDP6-LISTEN:2345                | Listen on IPv6/UDP      |

| socat - TCP6-LISTEN:PORT | socat - TCP6-LISTEN:2345                | Listen on IPv6/TCP      |

| socat - UDP-LISTEN:PORT  | socat - UDP-LISTEN:2345                 | Listen on IPv4/UDP      |

| socat - TCP-LISTEN:PORT  | socat - TCP-LISTEN:2345                 | Listen on IPv4/TCP      |

| iperf3 -PROTO -p PORT    | iperf3 -4 -p 2345                       | IPv4 iperf server       |

| -B IP -s                 | -B 10.0.0.42 -s                         |                         |

|                          | iperf3 -6 -p 2345                       | IPv6 iperf server       |

|                          | -B 2001:db8:42::42 -s                   |                         |

| iperf3 -PROTO -p PORT    | iperf3 -6 -p 2345                       | Connect to iperf server |

| -O IGNORETIME -t RUNTIME | -O 10 -t 190                            | Run for 190 seconds,    |

|                          |                                         | skip first 10 seconds   |

| -P PARALLEL -c IP        | -P20 -c 2001:db8:23::2a                 | with 20 sessions        |

|                          |                                         | connecting to           |

|                          |                                         | 2001:db8:23::2a         |

| iperf3 -PROTO -p PORT    |                                         | Same as above,          |

| -O IGNORETIME -t RUNTIME |                                         | but connect via UDP     |

| -P PARALLEL -c IP        |                                         |                         |

| -u -b0                   |                                         | [                       |

Table 3.2: NAT64 Verification Commands

| Address             | Description                                      |

|---------------------|--------------------------------------------------|

| 2001:db8:42::/64    | IPv6 host network                                |

| 2001:db8:23::/96    | IPv6 mapping to the IPv4 Internet                |

| 2001:db8:42::42     | IPv6 host address                                |

| 2001:db8:42::77     | IPv6 router address                              |

| 2001:db8:42::a00:2a | In-network IPv6 address mapped to 10.0.0.42 (p4) |

| 2001:db8:23::a00:2a | IPv6 address mapped to 10.0.0.42 (Tayga)         |

| 2001:db8:23::2a     | IPv6 address mapped to 10.0.0.42 (Jool)          |

Table 3.3: IPv6 Address and Network Overview

| Address                                  | Description                                            |

|------------------------------------------|--------------------------------------------------------|

| 10.0.0.0/24                              | IPv4 host network                                      |

| 10.0.1.0/24 IPv4 network mapping to IPv6 |                                                        |

| 10.0.0.77 IPv4 router address            |                                                        |

| 10.0.0.66                                | In-network IPv4 address mapped to 2001:db8:42::42 (p4) |

| 10.0.1.42                                | IPv4 address mapped to 2001:db8:42::42 (Tayga)         |

| 10.0.1.66                                | IPv4 address mapped to 2001:db8:42::42 (Jool)          |

Table 3.4: IPv4 Address and Network Overview

# **Chapter 4**

# Results

This section describes the achieved results and compares the P4 based implementation with real world software solutions.

We distinguish the software implementation of P4 (BMV2) and the hardware implementation (NetFPGA) due to significant differences in deployment and development. We present benchmarks for the existing software solutions as well as for our hardware implementation. As the objective of this thesis is to demonstrate the high speed capabilities of NAT64 in hardware, no benchmarks were performed on the P4 software implementation.

# 4.1 P4 Based Implementations

We successfully implemented P4 code to realise NAT64 [52]. It contains parsers for all related protocols (IPv6, IPv4, UDP, TCP, ICMP, ICMP6, NDP, ARP), supports EAMT as defined by RFC7757 [3], and is feature equivalent to the two compared software solutions Tayga [29] and Jool [31]. Due to limitations in the P4 environment of the NetFPGA environment, the BMV2 implementation is more feature rich.

For this thesis the parsing capabilities of P4 were adequate. However P4, at the time of writing, cannot parse ICMP6 options in general, as the upper level protocol does not specify the number of option blocks that follow. Parsing of an unspecified number of 64 bit blocks is required, which P4 does not support.

The language has some limitations on the placement of conditional statements (if/switch).<sup>1</sup> Furthermore P4/BMV2 does not support for multiple LPM keys in a table, however it supports multiple keys with ternary matching, which is a superset of LPM matching.

When developing P4 programs, the reason for incorrect behaviour we have seen were checksum problems. This is in retrospective expected, as the main task of our implementation is modifying headers on which the checksums depend. In all cases we have seen Ethernet frame checksum errors, the effective length of the packet was incorrect.

The tooling around P4 is somewhat fragile. We encountered small language bugs during the development [50], (compare section B.4) or found missing features [49], [55]: it is at the moment impossible to retrieve the matching key from table or the name of the action called. Thus if different table entries call the same action, it is impossible within the action, or if forwarded to the controller, within the controller to distinguish on which match the action was triggered. This problem is very consistent within P4, not even the matching table name can be retrieved. While these information can be added manually as additional fields in the table entries, we would expect a language to support reading and forwarding this kind of meta information.

While in P4 the P4 code and the related controller are tightly coupled, their data definitions are not. Thus the packet format definition that is used between the P4 switch and the controller has to be duplicated. Our experiences in software development indicate that this duplication is a likely source of errors in bigger software projects.

The supporting scripts in the P4 toolchain are usually written in python2. However, python2 "is legacy" [59]. During development errors with unicode string handling in python2 caused changes to IPv6 addresses.

<sup>&</sup>lt;sup>1</sup> In general, if and switch statements in actions lead to errors, but not all constellations are forbidden.

### 4.2 P4/BMV2

The software implementation of P4 has most features, which is mostly due to the capability of creating checksums over the payload. It enables the switch to act as a "proper" participant in NDP, as this requires the host to calculate checksums over the payload. Table 4.1 references all implemented features. The switch responds to ICMP echo requests, ICMP6 echo requests,

| Feature              | Description                                                | Status                         |

|----------------------|------------------------------------------------------------|--------------------------------|

| Switch to controller | Switch forwards unhandled packets to controller            | fully implemented <sup>a</sup> |

| Controller to Switch | Controller can setup table entries                         | fully implemented <sup>b</sup> |

| NDP                  | Switch responds to ICMP6 neighbor                          |                                |

|                      | solicitation request (without controller)                  | fully implemented <sup>c</sup> |

| ARP                  | Switch can answer ARP request (without controller)         | fully implemented <sup>d</sup> |

| ICMP6                | Switch responds to ICMP6 echo request (without controller) | fully implemented <sup>e</sup> |

| ICMP                 | Switch responds to ICMP echo request (without controller)  | fully implemented <sup>f</sup> |

| NAT64: TCP           | Switch translates TCP with checksumming                    |                                |

|                      | from/to IPv6 to/from IPv4                                  | fully implemented <sup>g</sup> |

| NAT64: UDP           | Switch translates UDP with checksumming                    |                                |

|                      | from/to IPv6 to/from IPv4                                  | fully implemented <sup>h</sup> |

| NAT64:               | Switch translates echo request/reply                       |                                |

| ICMP/ICMP6           | from/to ICMP6 to/from ICMP with checksumming               | fully implemented <sup>i</sup> |

| NAT64: Sessions      | Switch and controller create 1:n sessions/mappings         | fully implemented <sup>j</sup> |

| Delta Checksum       | Switch can calculate checksum without payload inspection   | fully implemented <sup>k</sup> |

| Payload Checksum     | Switch can calculate checksum with payload inspection      | fully implemented <sup>1</sup> |

```

**Source code: actions_egress.p4

**bSource code: controller.py

**Source code: actions_icmp6_ndp_icmp.p4

**Source code: actions_arp.p4

**Source code: actions_icmp6_ndp_icmp.p4

**Source code: actions_icmp6_ndp_icmp.p4

**Source code: actions_icmp6_ndp_icmp.p4

**Source code: actions_nat64_generic_icmp.p4

**Source code: actions_nat64_generic_icmp.p4

**Source code: actions_nat64_generic_icmp.p4

**Source code: actions_nat64_session.p4, controller.py

**Source code: actions_delta_checksum.p4

**Source code: actions_delta_checksum.p4

**Source code: checksum_bmv2.p4

```

Table 4.1: P4/BMV2 Feature List

answers NDP and ARP requests. Overall P4/BMV is very easy to use, even without a controller a fully functional network host can be implemented.

This P4/BMV implementation supports translating ICMP/ICMP6 echo request and echo reply messages, but does not support all ICMP/ICMP6 translations that are defined in RFC6145 [28].

#### 4.3 P4/NetFPGA

In the following section we describe the achieved feature set of P4/NetFPGA in detail and analyse differences to the BMV2 based implementation.

#### 4.3.1 Features

While the NetFPGA target supports P4, compared to P4/BMV2 we only implemented a reduced features set on P4/NetPFGA. The first reason for this is missing support of the NetFPGA P4 compiler to inspect payload and to compute checksums over payload. While this can (partially) be compensated using delta checksums, the compile time of 2 to 6 hours contributed to a significant slower development cycle compared to BMV2. Lastly, the focus of this thesis is to

4.3 P4/NetFPGA 35

implement high speed NAT64 on P4, which only requires a subset of the features that we realised on BMV2. In table 4.2 we summarise the implemented features and reason about their portability afterwards: The switch to controller communication differs, because the P4/NetFPGA

| Feature              | Description                                                | Status                         |

|----------------------|------------------------------------------------------------|--------------------------------|

| Switch to controller | Switch forwards unhandled packets to controller            | portable                       |

| Controller to Switch | Controller can setup table entries                         | portable                       |

| NDP                  | Switch responds to ICMP6 neighbor                          |                                |

|                      | solicitation request (without controller)                  | portable                       |

| ARP                  | Switch can answer ARP request (without controller)         | portable                       |

| ICMP6                | Switch responds to ICMP6 echo request (without controller) | portable                       |

| ICMP                 | Switch responds to ICMP echo request (without controller)  | portable                       |

| NAT64: TCP           | Switch translates TCP with checksumming                    |                                |

|                      | from/to IPv6 to/from IPv4                                  | fully implemented <sup>a</sup> |

| NAT64: UDP           | Switch translates UDP with checksumming                    |                                |

|                      | from/to IPv6 to/from IPv4                                  | fully implemented <sup>b</sup> |

| NAT64:               | Switch translates echo request/reply                       |                                |

| ICMP/ICMP6           | from/to ICMP6 to/from ICMP with checksumming               | portable                       |

| NAT64: Sessions      | Switch and controller create 1:n sessions/mappings         | portable                       |

| Delta Checksum       | Switch can calculate checksum without payload inspection   | fully implemented <sup>c</sup> |

| Payload Checksum     | Switch can calculate checksum with payload inspection      | unsupported                    |

aSource code: actions\_nat64\_generic\_icmp.p4

Table 4.2: P4/NetFPGA Feature List

implementation does not have the clone3() extern that the BMV2 implementation offers. However communication to the controller can easily be realised by using one of the additional ports of the NetFPGA and connect a physical network card to it.

Communicating from the controller towards the switch also differs, as the p4utils suite supporting BMV2 offers an easy access to the switch tables. While the P4-NetFPGA support repository also offers python scripts to modify the switch tables, the code is less sophisticated and more fragile. While porting the existing code is possible, it might be of advantage to rewrite parts of the P4-NetFPGA before.

The NAT64 session support is based on the P4 switch communicating with the controller and vice versa. As we consider both features to be portable, we also consider the NAT64 session feature to be portable.

P4/NetFPGA does not offer calculating the checksum over the payload and thus calculating the checksum over the payload creating a reply for an neighbor solicitation packet is not possible. However, as the payload stays the same as in the request, our delta based checksum approach can be reused in this situation. With the same reasoning we consider our ICMP6 and ICMP code, which also requires to create payload based checksums, to be portable.

ARP replies do not contain a checksum over the payload, thus the existing ARP code can be directly integrated into P4/NetFPGA without any changes.

While the P4/NetFPGA target currently does not support accessing the payload or creating checksums over it, there are two possibilities to extend the platform: either by creating an HDL module or by modifying the generated PX program. [51] Due to the existing code complexity of the P4/NetFPGA platform, using the HDL module based approach is likely to be more sustainable.

#### 4.3.2 Stability

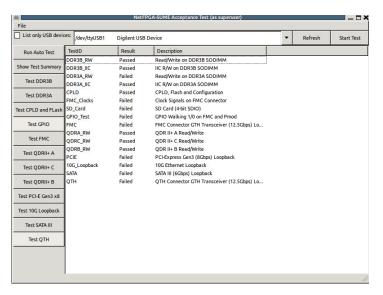

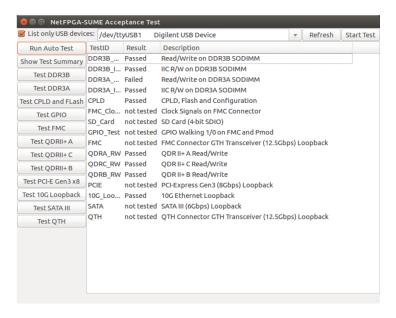

Two different NetPFGA cards were used during the development of this thesis. The first card had consistent ioctl errors (compare section B.4) when writing table entries. The available hardware tests (compare figures 4.1 and 4.2) showed failures in both cards, however the first card reported an additional "10G\_Loopback" failure. Due to the inability of setting table entries, no

bSource code: actions\_nat64\_generic\_icmp.p4

$<sup>{}^{</sup>c}\textbf{Source code} \hbox{: actions\_delta\_checksum.p4}$

benchmarking was performed on the first NetFPGA card. During the development and bench-

Figure 4.1: Hardware Test NetPFGA Card 1

Figure 4.2: Hardware Test NetPFGA Card 2 [22]

marking, the second NetFPGA card stopped to function properly multiple times. In theses cases the card would not forward packets anymore. Multiple reboots (up to 3) and multiple times reflashing the bitstream to the NetFPGA usually restored the intended behaviour. However due to this "crashes", it was impossible for us to run a benchmark for more than one hour. Similarly, sometimes flashing the bitstream to the NetFPGA would fail. It was required to reboot the host containing the NetFPGA card up to 3 times to enable successful flashing.<sup>2</sup>

#### **Performance**

The NetFPGA card performed at near line speed and offers NAT64 translations at 9.28 Gbit/s (see section 4.5 for details). Single and multiple streams performed almost exactly identical and have been consistent through multiple iterations of the benchmarks.

<sup>&</sup>lt;sup>2</sup>Typical output of the flashing process would be: "fpga configuration failed. DONE PIN is not HIGH"

4.3 P4/NetFPGA 37

### 4.3.3 Usability

The handling and usability of the NetFPGA card is rather difficult. In this section we describe our findings and experiences with the card and its toolchain.

To use the NetFPGA, the tools Vivado and SDNET provided by Xilinx need to be installed. However a bug in the installer triggers an infinite loop, if a certain shared library<sup>3</sup> is missing on the target operating system. The installation program seems to be still progressing, however never finishes.

While the NetFPGA card supports P4, the toolchains and supporting scripts are in an immature state. The compilation process consists of at least 9 different steps, which are interdependent.<sup>4</sup> Some of the steps generate shell scripts and python scripts that in turn generate JSON data.<sup>5</sup> However incorrect parsing generates syntactically incorrect scripts or scripts that generate incorrect output. The toolchain provided by the NetFPGA-P4 repository contains more than 80000 lines of code. The supporting scripts for setting table entries require setting the parameters for all possible actions, not only for the selected action. Supplying only the required parameters results in a crash of the supporting script.

The documentation for using the NetFPGA-P4 repository is very distributed and does not contain a reference on how to use the tools. Mapping of egress ports and their metadata field are found in a python script that is used for generating test data.

The compile process can take up to 6 hours and because the different steps are interdependent, errors in a previous stage were in our experiences detected hours after they happened. The resulting log files of the compilation process can be up to 5 MB in size. Within this log file various commands output references to other logfiles, however the referenced logfiles do not exist before or after the compile process.

During the compile process various informational, warning and error messages are printed. However some informational messages constitute critical errors, while on the other hand critical errors and syntax errors often do not constitute a critical error.<sup>6</sup> Also contradicting output is generated.<sup>7</sup>

Programs or scripts that are called during the compile process do not necessarily exit non zero if they encountered a critical error. Thus finding the source of an error can be difficult due to the compile process continuing after critical errors occurred. Not only programs that have critical errors exit "successfully", but also python scripts that encounter critical paths don't abort with raise(), but print an error message to stdout and don't abort with an error.

The most often encountered critical compile error is "Run 'impl\_1' has not been launched. Unable to open". This error indicates that something in the previous compile steps failed and can refer to incorrectly generated testdata to unsupported LPM tables.

The NetFPGA kernel module provides access to virtual Linux devices (nf0...nf3). However tcp-dump does not see any packets that are emitted from the switch. The only possibility to capture packets that are emitted from the switch is by connecting a physical cable to the port and capturing on the other side.

Jumbo frames<sup>8</sup> are commonly used in 10 Gbit/s networks. According to [63], even many gigabit network interface card support jumbo frames. However according to emails on the private NetPFGA mailing list, the NetFPGA only supports 1500 byte frames at the moment and additional work is required to implement support for bigger frames.

Our P4 source code requires to contains Xilinx annotations<sup>9</sup> that define the maximum packet size in bits. We observed two different errors on the output packet, if the incoming packets exceed the maximum packet size:

<sup>&</sup>lt;sup>3</sup>The required shared library is libncurses5.

<sup>&</sup>lt;sup>4</sup>See source code bin/do-all-steps.sh.

<sup>&</sup>lt;sup>5</sup>One compilation step calls the script "config\_writes.py". This script failed with a syntax error, as it contained incomplete python code. The scripts config\_writes.py and config\_writes.sh are generated by gen\_config\_writes.py. The output of the script gen\_config\_writes.py depends on the content of config\_writes.txt. That file is generated by the simulation "xsim". The file "SimpleSumeSwitch\_tb.sv" contains code that is responsible for writing config\_writes.txt and uses a function named axi4\_lite\_master\_write\_request\_control for generating the output. This in turn is dependent on the output of a script named gen\_testdata.py.

<sup>&</sup>lt;sup>6</sup>F.i. "CRITICAL WARNING: [BD 41-737] Cannot set the parameter TRANSLATION\_MODE on /axi\_interconnect\_0. It is read-only." is a non critical warning.

<sup>&</sup>lt;sup>7</sup>While using version 2018.2, the following message was printed: "WARNING: command 'get\_user\_parameter' will be removed in the 2015.3 release, use 'get\_user\_parameters' instead".

<sup>&</sup>lt;sup>8</sup>Frames with an MTU greater than 1500 bytes.

<sup>&</sup>lt;sup>9</sup>F.i. "@Xilinx\_MaxPacketRegion(1024)"

- The output packet is longer than the original packet.

- The output packet is corrupted.

While most of the P4 language is supported on the NetFPGA, some key techniques are currently missing or not supported.

- Analysing / accessing payload is not supported

- · Checksum computation over payload is not supported

- Using LPM tables can lead to compilation errors

- Depending on the match type, only certain table sizes are allowed

Renaming variables in the declaration of the parser or departer lead to compilation errors. The P4 function syntax is not supported. For this reason our implementation uses #define statements instead of functions.

### 4.4 Software Based NAT64

Both solutions Tayga and Jool worked flawlessly. However as expected, both solutions are CPU bound. Under high load scenarios both solutions utilise one core fully. Neither Tayga as a user space program nor Jool as a kernel module implement multi threading.

### 4.5 NAT64 Benchmarks

In this section we give an overview of the benchmark design and summarise the benchmarking results.

## 4.5.1 Benchmark Design

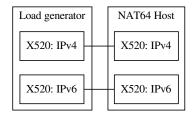

Figure 4.3: Benchmark Design for NAT64 in Software Implementations

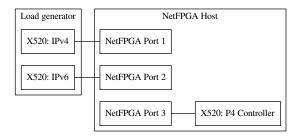

We use two hosts for performing benchmarks: a load generator and a NAT64 translator. Both hosts are equipped with a dual port Intel X520 10 Gbit/s network card. Both hosts are connected using DAC without any equipment in between. TCP offloading is enabled in the X520 cards. Figure 4.3 shows the network setup. When testing the NetPFGA/P4 performance, the X520 cards in the NAT64 translator are disconnected and instead the NetPFGA ports are connected, as shown in figure 4.4. The load generator is equipped with a quad core CPU (Intel(R) Core(TM) i7-6700 CPU @ 3.40GHz), enabled with hyperthreading and 16 GB RAM. The NAT64 translator is also equipped with a quard core CPU (Intel(R) Core(TM) i7-4770 CPU @ 3.40GHz) and 16 GB RAM. The first 10 seconds of the benchmark are excluded to avoid the TCP warm up phase.<sup>10</sup>

<sup>&</sup>lt;sup>10</sup>iperf -O 10 parameter, see section 3.6.

Figure 4.4: NAT64 with NetFPGA Benchmark

## 4.5.2 Benchmark Summary

Overall **Tayga** has shown to be the slowest translator with an achieved bandwidth of **about 3 Gbit/s**, followed by **Jool** that translates at about **8 Gbit/s**. **Our solution** is the fastest with an almost line rate translation speed of about **9 Gbit/s** (compare tables 4.3 and 4.4).

The TCP based benchmarks show realistic numbers, while iperf reports above line rate speeds (up to 22 gbit/s on a 10gbit/s link) for UDP based benchmarks. For this reason we have summarised the UDP based benchmarks with their average loss instead of listing the bandwidth details. The "adjusted bandwidth" in the UDP benchmarks incorporates the packets loss (compare tables 4.5 and 4.6).

Both software solutions showed significant loss of packets in the UDP based benchmarks (Tayga: up to 91%, Jool up to 71%), while the P4/NetFPGA showed a maximum of 0.01% packet loss. Packet loss is only recorded by iperf for UDP based benchmarks, as TCP packets are confirmed and resent if necessary.

Tayga has the highest variation of results, which might be due to being fully CPU bound, even in the non-parallel benchmark. Jool has less variation and in general the P4/NetFPGA solution behaves almost identical in different benchmark runs.

The CPU load for TCP based benchmarks with Jool was almost negligible, however for UDP based benchmarks one core was almost 100% utilised. In all benchmarks with Tayga, one CPU was fully utilised. When the translation for P4/NetFPGA happens within the NetFPGA card, there was no CPU utilisation visible on the NAT64 host.

We see lower bandwidth for translating IPv4 to IPv6 in all solutions. We suspect that this might be due to slighty increasing packet sizes that occur during this direction of translation. Not only does this vary the IPv4 versus IPv6 bandwidth, but it might also cause fragmentation that slows down.

During the benchmarks with up to 10 parallel connections, no significant CPU load was registered on the load generator. However with 20 parallel connections, each of the two iperf processes<sup>11</sup> partially spiked to 100% CPU usage. With 50 parallel connections the CPU load of each process hit 100% often. For this reason we argue that the benchmark results of the benchmarks with 20 or more parallel connections might be affected by the load generator limits. While there is no visible evidence in our results, this problem might become more significant with higher speed links.

While Tayga's performance is reduced with the growing number of parallel connections, both Jool and our P4/NetFPGA implementations vary only slighty.

Overall the performance of Tayga, a Linux user space program, is as expected. We were surprised about the good performance of Jool, which, while slower than the P4/NetFPGA solution, is almost on par with our solution.

<sup>&</sup>lt;sup>11</sup>The client process for sending, the server process for receiving.

| Implementation       | min/avg/max in Gbit/s |                    |                    |                    |

|----------------------|-----------------------|--------------------|--------------------|--------------------|

| Tayga                | 2.79 / 3.20 / 3.43    | 3.34 / 3.36 / 3.38 | 2.57 / 3.02 / 3.27 | 2.35 / 2.91 / 3.20 |

| Jool                 | 8.22 / 8.22 / 8.22    | 8.21 / 8.21 / 8.22 | 8.21 / 8.23 / 8.25 | 8.21 / 8.23 / 8.25 |

| P4 / NetPFGA         | 9.28 / 9.28 / 9.29    | 9.28 / 9.28 / 9.29 | 9.28 / 9.28 / 9.29 | 9.28 / 9.28 / 9.29 |

| Parallel connections | 1                     | 10                 | 20                 | 50                 |

Table 4.3: IPv6 to IPv4 TCP NAT64 Benchmark

| Implementation       | min/avg/max in Gbit/s |                    |                    |                    |

|----------------------|-----------------------|--------------------|--------------------|--------------------|

| Tayga                | 2.90 / 3.15 / 3.34    | 2.87 / 3.01 / 3.22 | 2.68 / 2.85 / 3.09 | 2.60 / 2.78 / 2.88 |

| Jool                 | 7.18 / 7.56 / 8.24    | 7.97 / 8.05 / 8.09 | 8.05 / 8.08 / 8.10 | 8.10 / 8.12 / 8.13 |

| P4 / NetPFGA         | 8.51 / 8.53 / 8.55    | 9.28 / 9.28 / 9.29 | 9.29 / 9.29 / 9.29 | 9.28 / 9.28 / 9.29 |

| Parallel connections | 1                     | 10                 | 20                 | 50                 |

Table 4.4: IPv4 to IPv6 TCP NAT64 Benchmark

| Implementation       | avg bandwidth in gbit/s / avg loss / adjusted bandwith |                   |                    |                    |

|----------------------|--------------------------------------------------------|-------------------|--------------------|--------------------|

| Tayga                | 8.02 / 70% / 2.43                                      | 9.39 / 79% / 1.97 | 15.43 / 86% / 2.11 | 19.27 / 91% 1.73   |

| Jool                 | 6.44 / 0% / 6.41                                       | 6.37 / 2% / 6.25  | 16.13 / 64% / 5.75 | 20.83 / 71% / 6.04 |

| P4 / NetPFGA         | 8.28 / 0% / 8.28                                       | 9.26 / 0% / 9.26  | 16.15 / 0% / 16.15 | 15.8 / 0% / 15.8   |

| Parallel connections | 1                                                      | 10                | 20                 | 50                 |

Table 4.5: IPv6 to IPv4 UDP NAT64 Benchmark

| Implementation       | avg bandwidth in gbit/s / avg loss / adjusted bandwith |                   |                    |                    |

|----------------------|--------------------------------------------------------|-------------------|--------------------|--------------------|

| Tayga                | 6.78 / 84% / 1.06                                      | 9.58 / 90% / 0.96 | 15.67 / 91% / 1.41 | 20.77 / 95% / 1.04 |

| Jool                 | 4.53 / 0% / 4.53                                       | 4.49 / 0% / 4.49  | 13.26 / 0% / 13.26 | 22.57 / 0% / 22.57 |

| P4 / NetPFGA         | 7.04 / 0% / 7.04                                       | 9.58 / 0% / 9.58  | 9.78 / 0% / 9.78   | 14.37 / 0% / 14.37 |

| Parallel connections | 1                                                      | 10                | 20                 | 50                 |

Table 4.6: IPv4 to IPv6 UDP NAT64 Benchmark

## **Chapter 5**

## **Conclusion and Outlook**